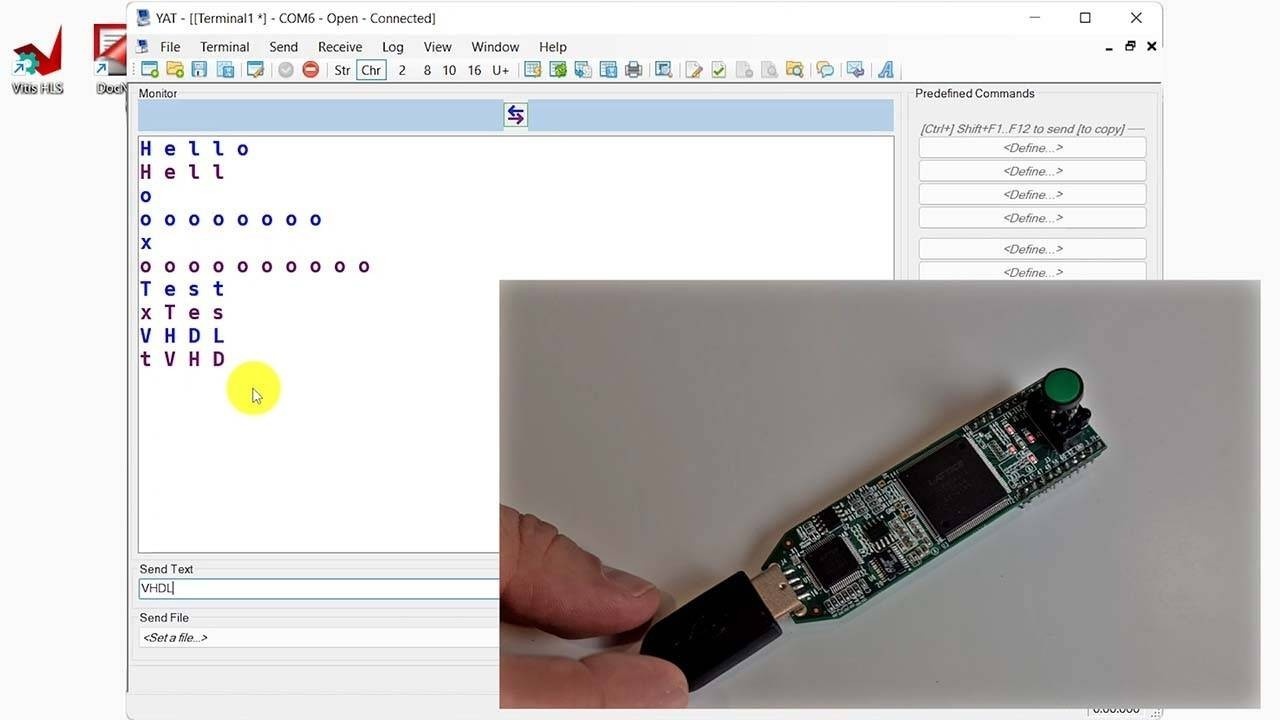

VHDLwhiz Membership

The FPGA learning experience that never ends

This VHDL training program supports you in becoming successful in programmable logic design.

When you join, you get access to everything in the portal, every tutorial, and every resource.

You get a new video tutorial series or resource item every month!

The tutorial is a course about a specific FPGA subject, while the resource can be a template, an example design, or something you can use to save time in your work.

I know that this concept works because most of the initial members have stayed since the launch in February 2021.

Join the community and build your confidence as an FPGA engineer! 😀

Scroll down to find out what the membership can do for you!

Why a membership site instead of another course?

There are many brilliant coding courses, all with the same limitations:

the learning curve is steep, and there is no support after it ends.

But FPGA design isn't something you ever get done learning.

You can always become better, and that's what the membership will reflect. I want to support you on the way to reaching your goals in digital hardware design.

A learning experience that doesn't end is appropriate for a learning curve that has no ceiling.

How the membership works

After you join, you can log in to the portal Dashboard to find all the content.

The new lessons will appear in the left sidebar. I will also announce them in the News tab, and I will send you an email so that you never miss anything.

Additionally, there is a Resources library that you can use for your convenience. I will reference the resources in the tutorials to keep the videos short and on target.

We also have a Core Training series to make it easy for you in the beginning and a Stages page with assessments to track your progress.

And finally, there is a Facebook group only for active members. I will use the group to communicate informally with you and the other members.

Resource Library

As a member, you get access to a collection of resources that you can use to save time in your work.

Currently, the forever-growing database consists of 66 items from five subcategories.

The templates, scripts, examples, printables, and video walkthroughs for installing software make it easy for you to get started on your next project.

Most of the example designs contain a ModelSim project that you can download and run on your computer within minutes.

I will reference the resources in the lessons to keep the tutorial videos short and on the topic.

New content every month

I will add a new tutorial series or resource item every month. You can view the content whenever you want, and you don't have to start at the beginning.

The membership is not a course; it's a learning program that supports you in achieving your goals in the long run.

Here's the current publishing schedule:

On the 1st of every even month (Feb, Apr, ..)

- New tutorial series

On the 1st of every odd month (Jan, Mar, ..)

- New resource item

You will receive an email when new content is available, and I will update the News section in the Membership portal.

Study at a pace that suits you.

Unlike a course, the membership has no beginning or end. Each tutorial series is a mini-course, and the resources are independent.

It's up to you how deep you want to immerse yourself into the world of programmable logic.

Scroll down to the "Get instant access to these tutorial series when you join" section to see the updated list of tutorials!

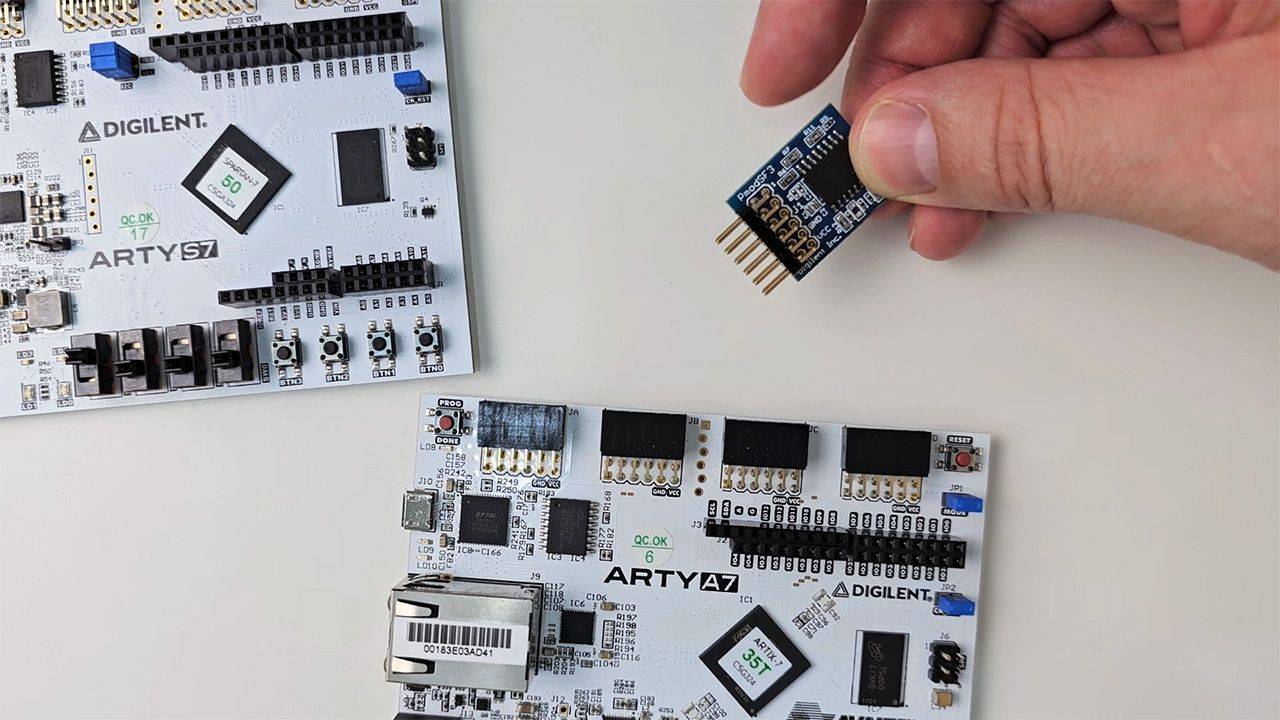

Do I need a specific development board?

Which software do I have to install?

How is it different from a course?

Can I get support from the instructor?

Can I cancel the subscription at any time?

Will the price increase?

What are the prerequisites?

My question is not listed in the FAQ

What's in the portal right now?

Currently, there are 36 courses available in the membership portal. That's because the membership has been going on since February 2021.

Additionally, there are 66 resource items (Templates and Scripts: 12, Example Designs: 20, Example Testbenches: 12, Printables: 5, Installation Guides: 14, Coding Challenges: 3).

Get instant access to these courses when you join:

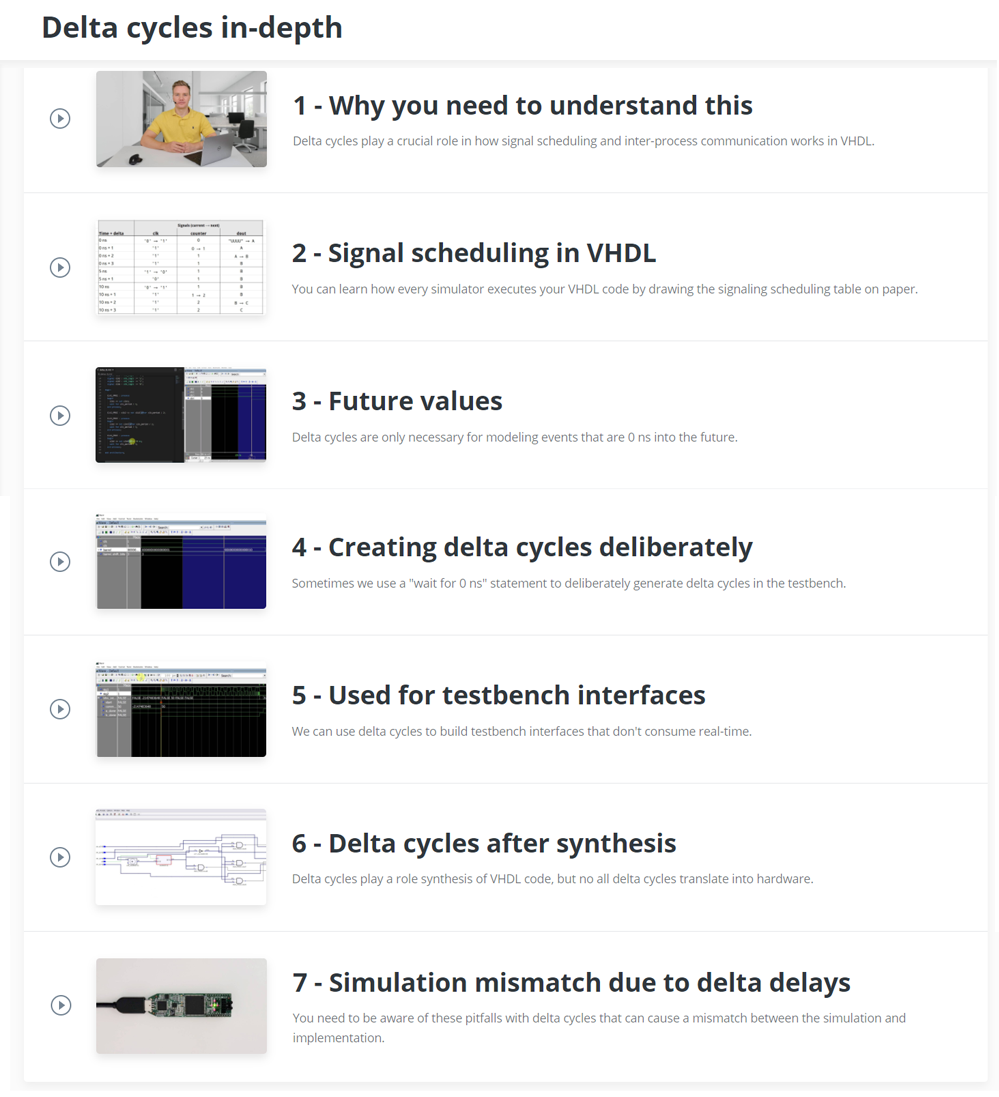

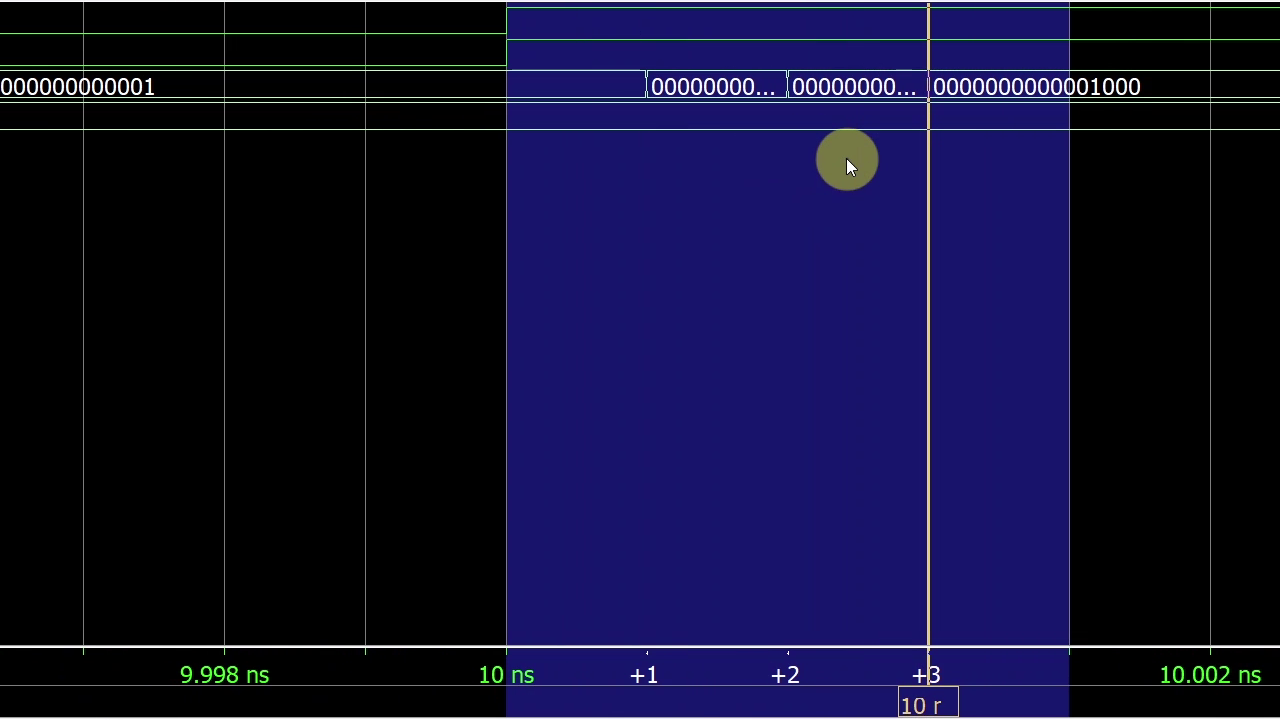

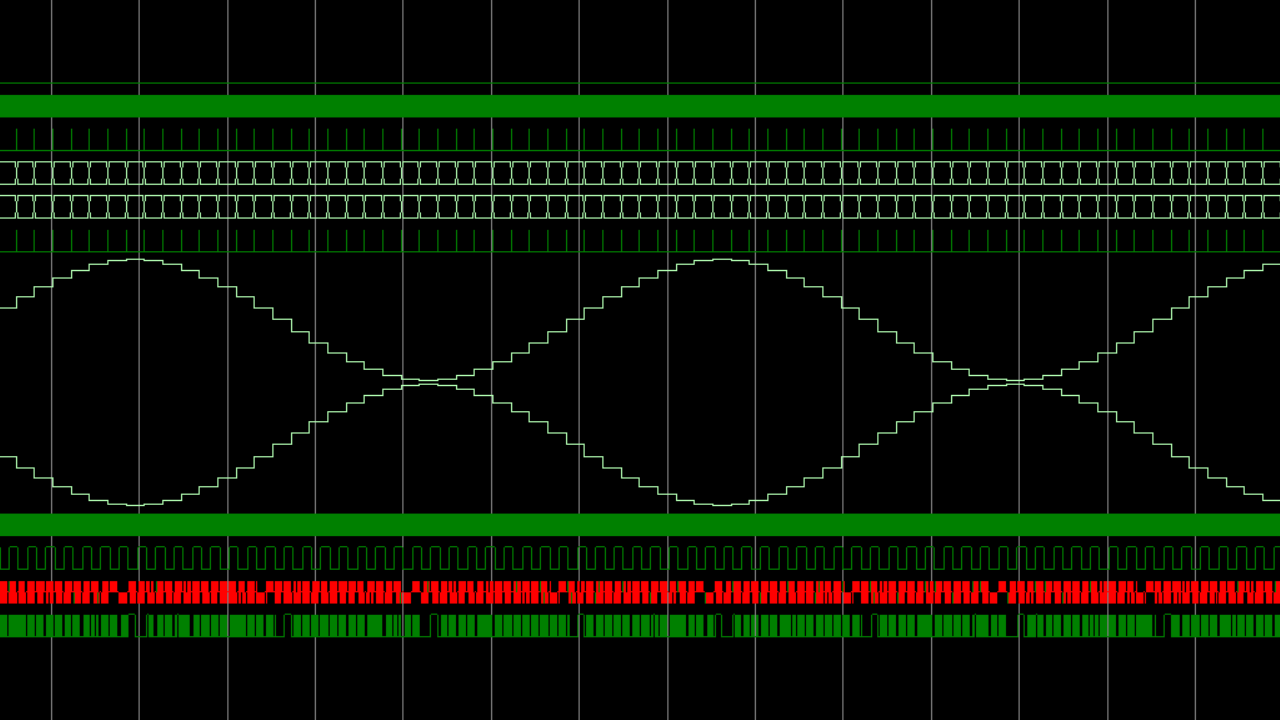

Delta cycles in-depth

Understanding how delta cycles work is key to becoming proficient in VHDL. This series teaches you how signal scheduling works in the simulator.

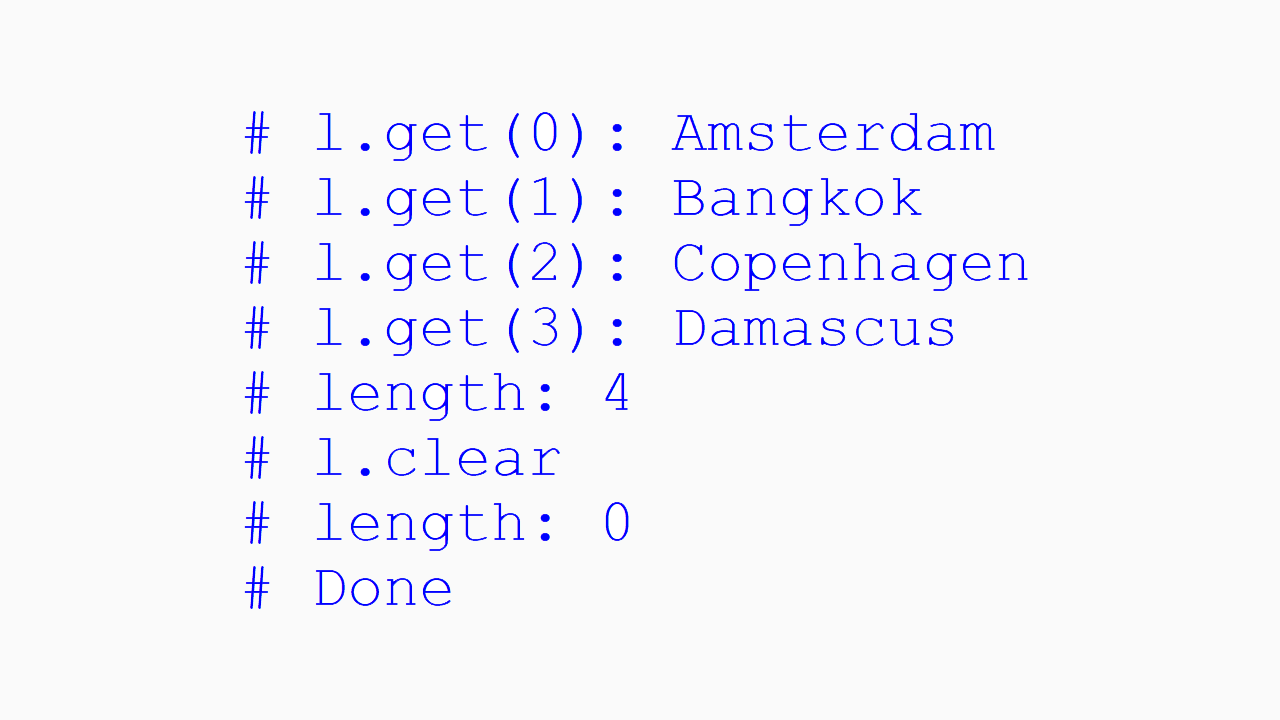

Protected type string list

In this series, we create a dynamic string list in VHDL based on Python's list class. We use a protected type to store strings of any length and quantity in the testbench.

ZedBoard audio pass-through

This tutorial series shows how to create a system-on-chip (SoC) design using Vivado and Vitis, enabling the ADAU1761 audio codec chip on the Xilinx ZedBoard.

I2S audio interface

In this tutorial series, we create an I2S interface module in VHDL. We'll use it for sending and receiving audio samples through the ADAU1761 audio codec chip on the Xilinx ZedBoard.

I2S BFM and self-checking TB

Learn how to create a self-checking testbench (TB) that uses a bus-functional model (BFM) to verify a serial transceiver device under test (DUT).

Makefile-based workflow for Lattice

Are you ready to ditch the GUI? In this series, we convert a Lattice iCEcube2 GUI project into a script-based workflow using a Makefile.

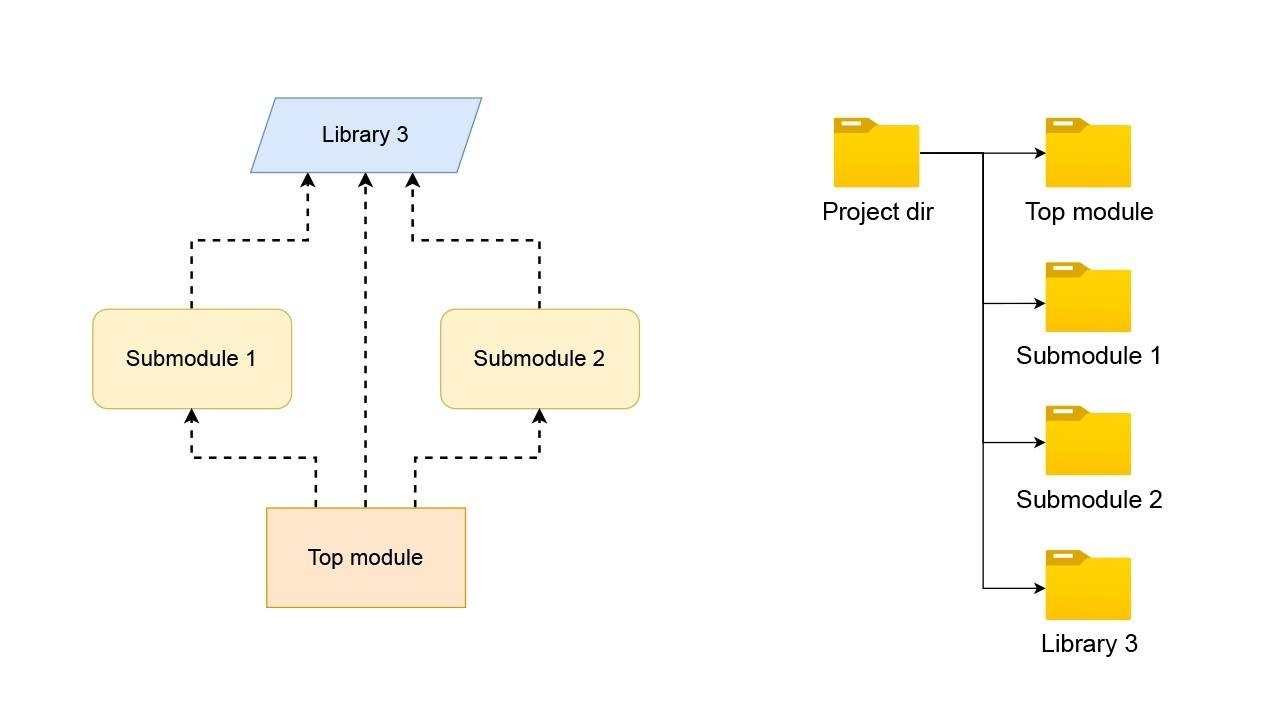

Script-based workflow

Learn how to structure a VHDL project consisting of multiple submodules. Use scripts to derive the compile order, launch simulations in batch mode and the GUI, and run regression tests.

Constrained random verification

This tutorial teaches how to achieve functional coverage with randomized interactions by using the OSVVM VHDL framework.

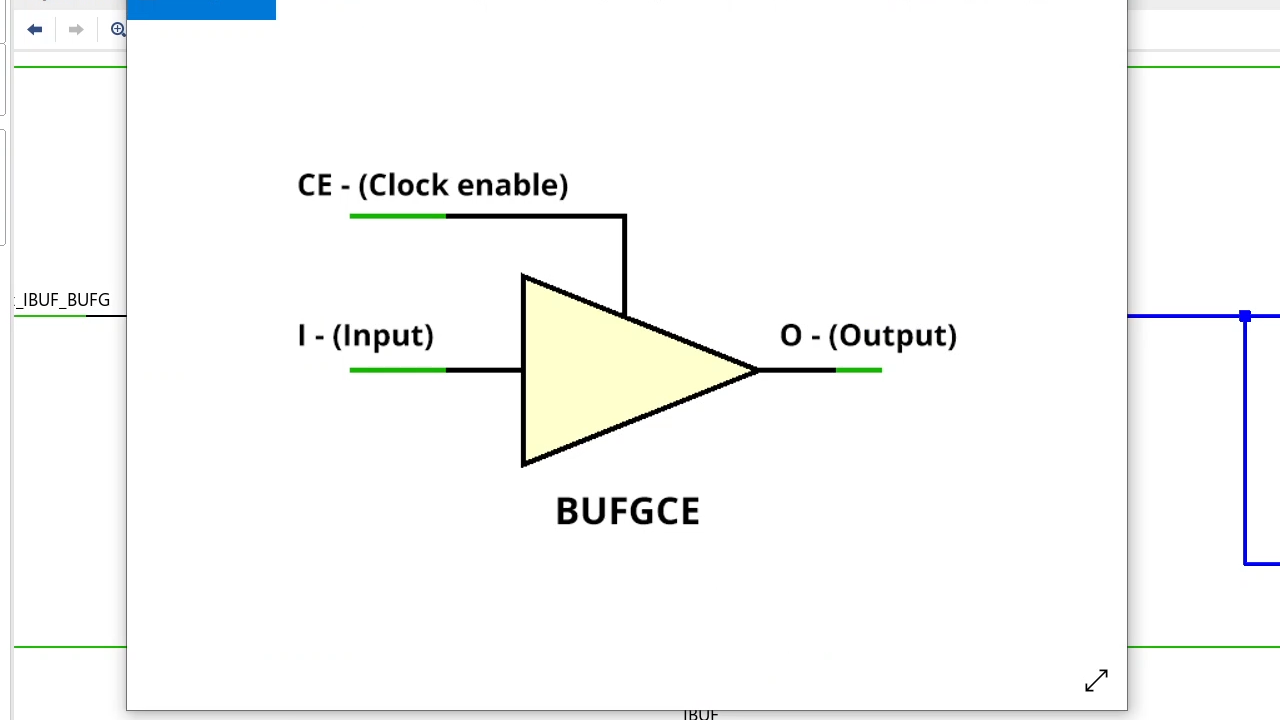

Clock divider

There are several ways to implement a clock divider in FPGAs. Some are superior to others, and after watching this series, you will know which to use.

SPI master for reading ambient light sensor

Learn to create an SPI master for reading an ambient light sensor from an FPGA. We also make an SPI slave BFM for simulating the ADC chip.

Advanced BFM signaling and transaction-based TB

Build a testbench that separates bit-level logic into separate modules and uses a command interface to control executor processes.

Run-length encoding

This lossless data compression algorithm is well suited for FPGAs because it requires few resources and works on data streams.

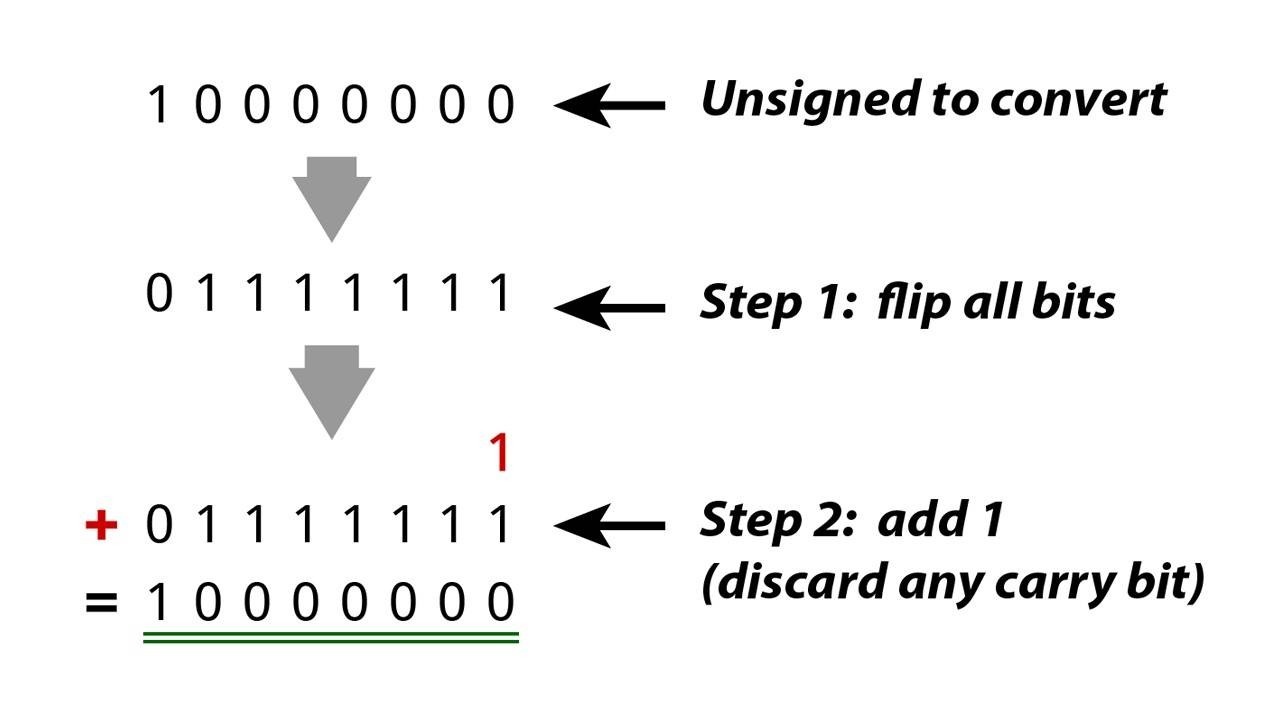

Numeric types

There are many beliefs about using numeric types like integer and real in RTL code. Let's find out precisely what the limitations are!

UVVM introduction

The Universal VHDL Verification Methodology (UVVM) framework provides a utility library, reusable verification components, and a way to structure your VHDL testbenches.

MicroBlaze SoC design

Learn how to build a system-on-chip (SoC) design by using a soft-core processor, existing IP cores, and your custom VHDL modules.

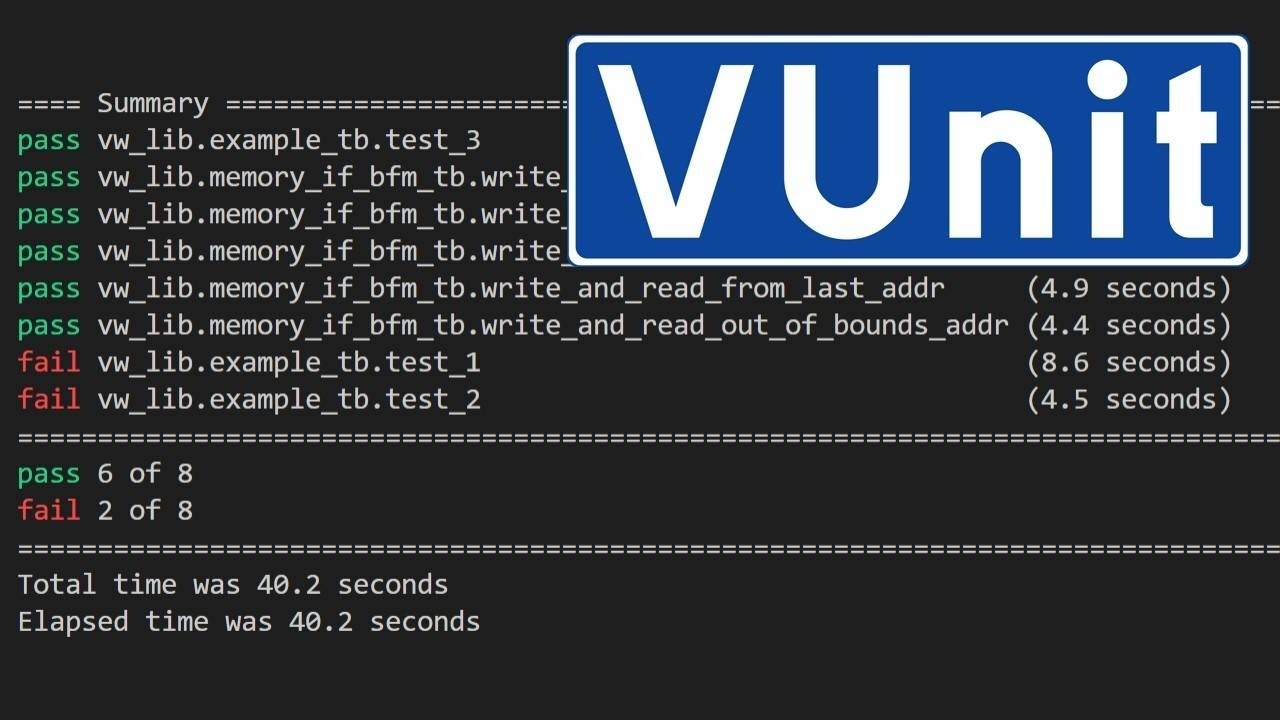

VUnit for structured testbench and advanced BFM design

Create neat testbenches and verification components using this testing framework's VHDL libraries. Automate your simulation flow with VUnit's Python test runner.

Image processing system and testbench design

Learn to develop high-speed image processing systems using VHDL. See how to simulate pixel filters using JPG pictures in a VHDL testbench.

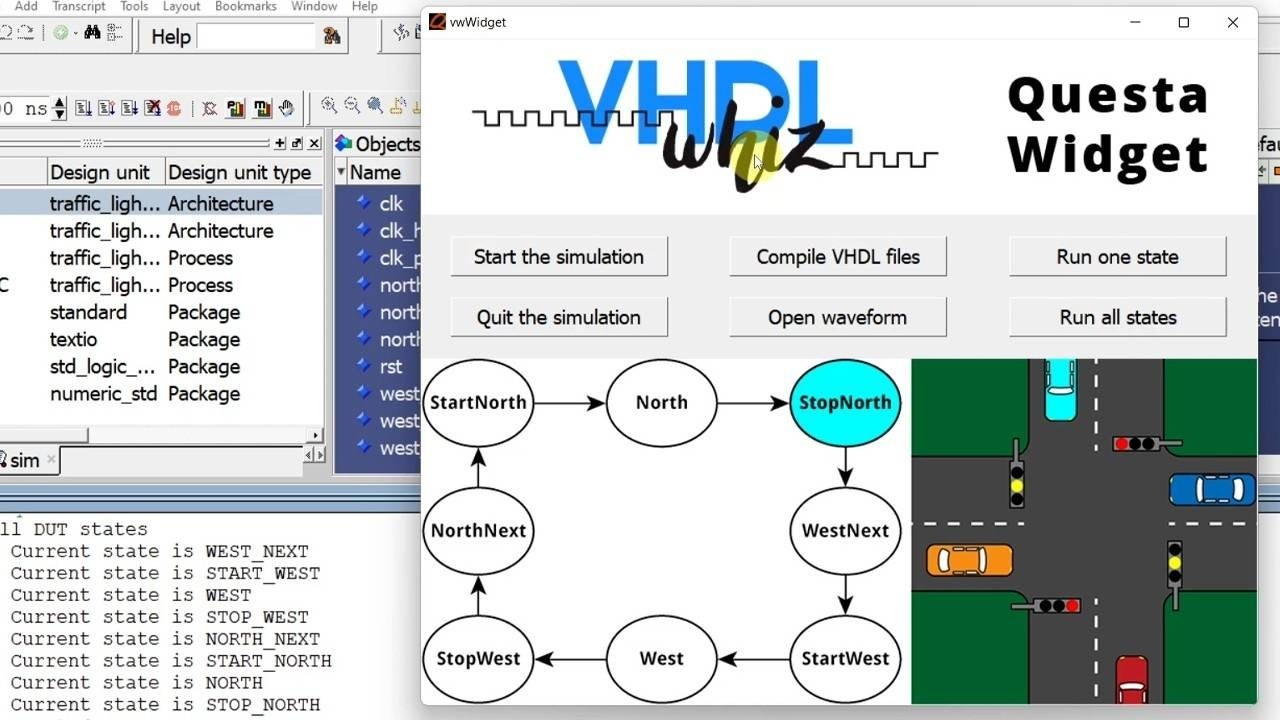

Tcl scripting for FPGA engineers

Learn the quirks of the Tool Command Language (Tcl) and see how to create a GUI widget for controlling a VHDL testbench in Questa/ModelSim.

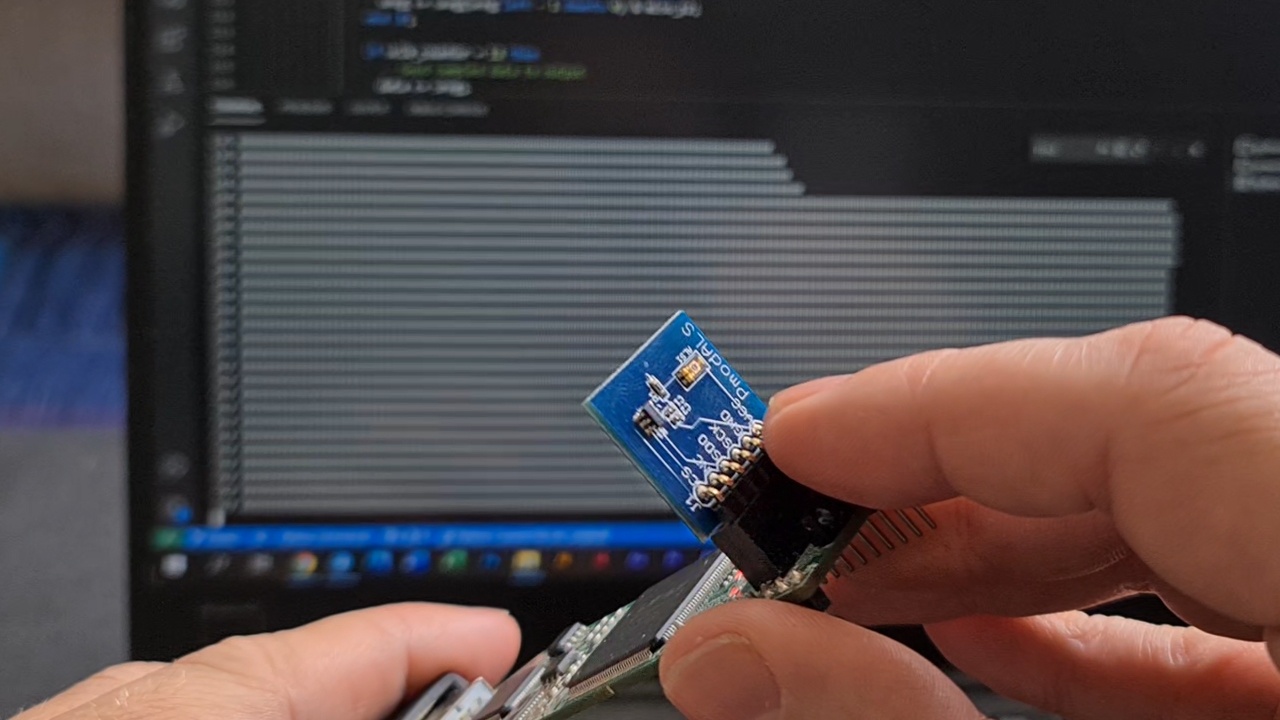

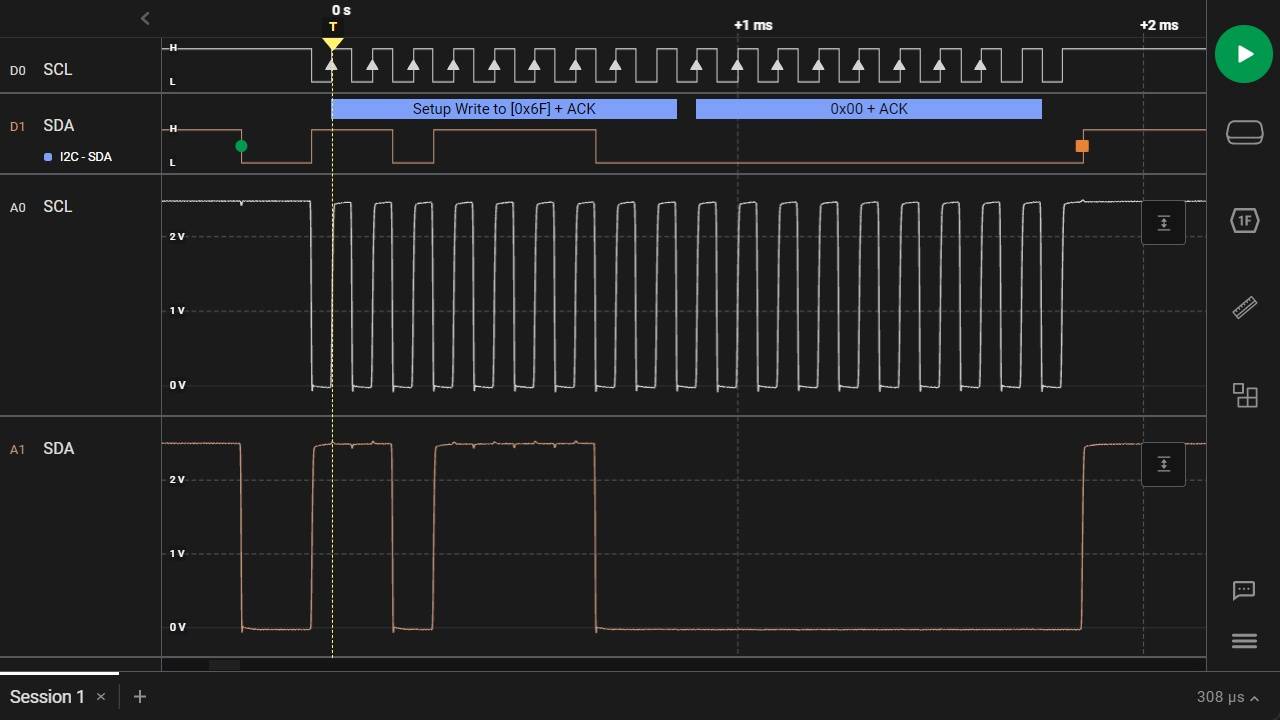

I²C controller for interfacing a real-time clock/calendar module in VHDL

Create an I²C controller (master) with AXI-style input and output buses. Implement the design on an FPGA board to set and read time and date values from the Digilent Pmod RTCC module over UART.

Combining VHDL frameworks: VUnit, UVVM, and OSVVM

You don't have to use only one VHDL verification framework. We can pick and choose the features we need and combine them to create awesome testbenches.

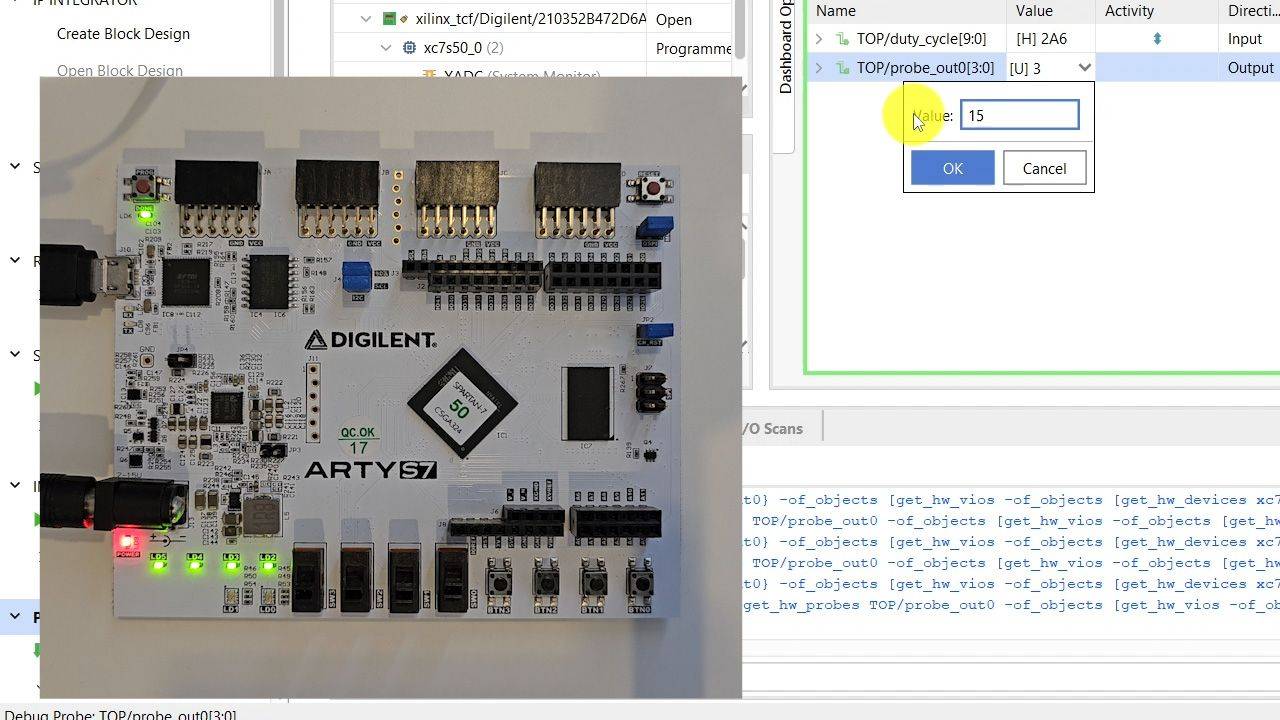

Tools for debugging VHDL designs

FPGA projects are challenging to debug, and that's because it's hard to understand what's going on in the design. But once we gain insight and see the complete picture, problems often melt away.

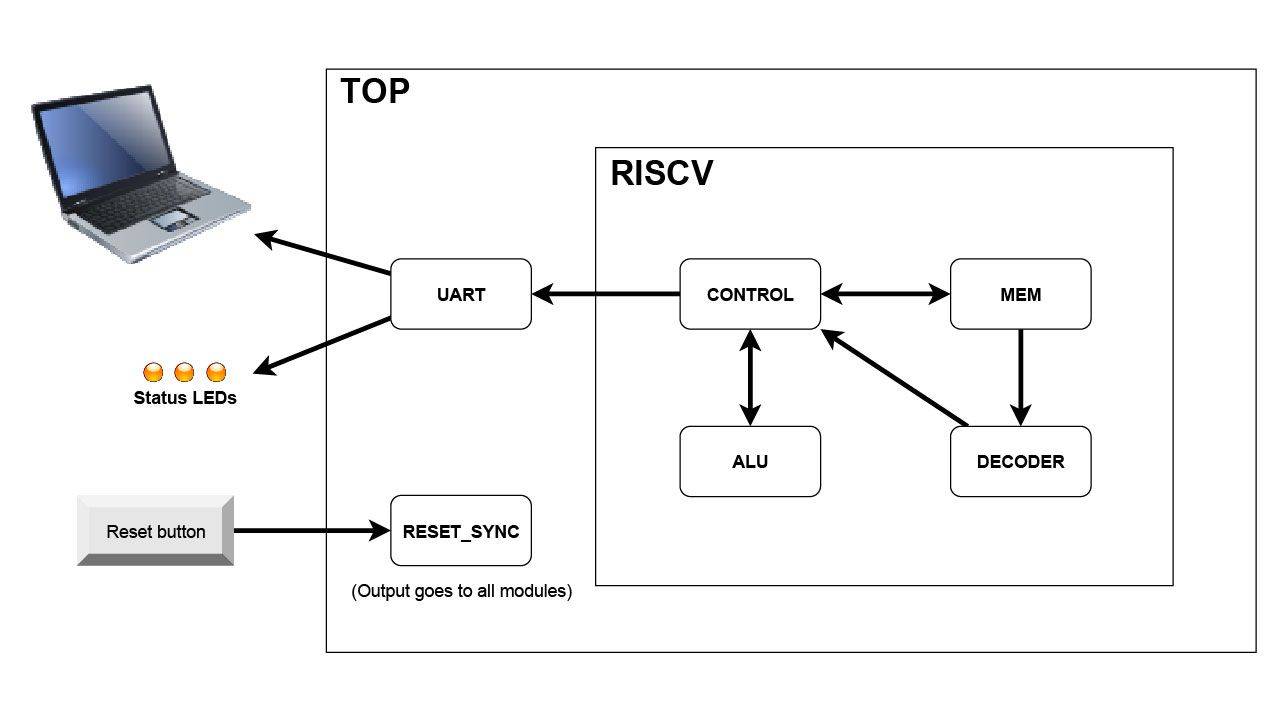

RISC-V processor Hello World!

Create a reduced instruction set computer using the RISC-V processor architecture. Learn how a CPU works by implementing one in VHDL and running it on the FPGA.

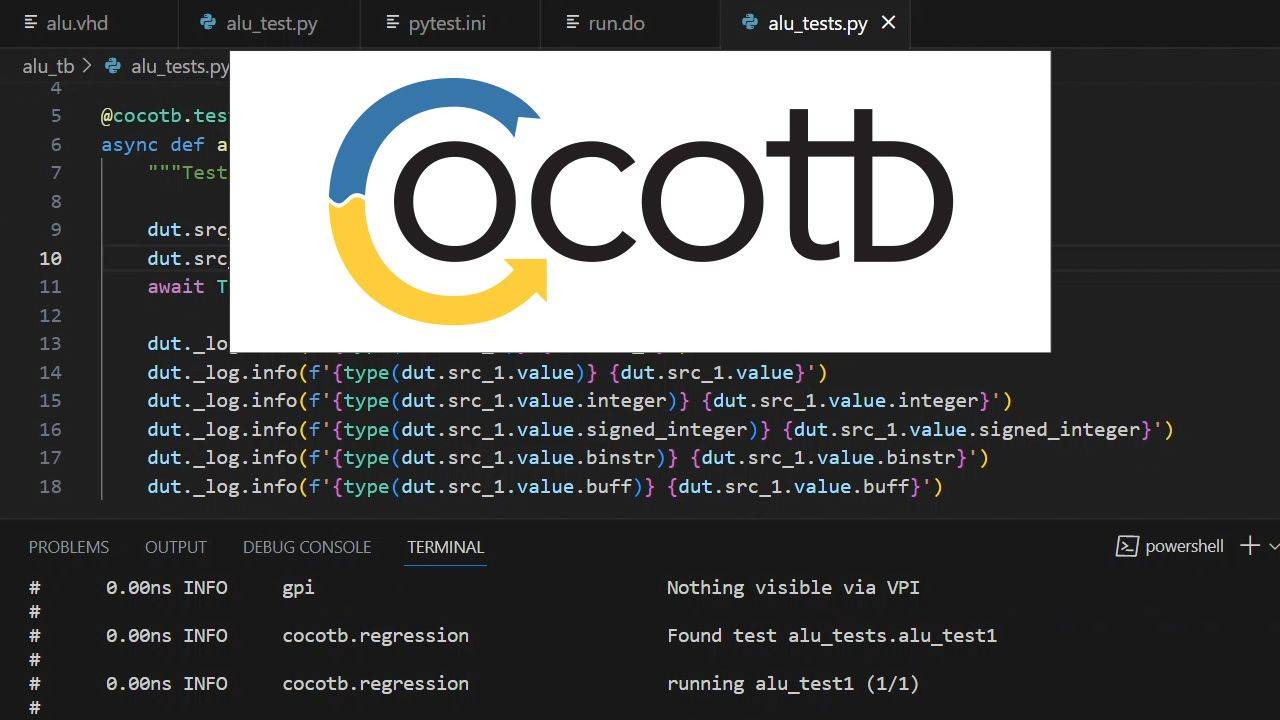

Cocotb introduction

Write testbenches in Python for your VHDL design with the Cocotb hardware verification framework. Learn to use Python's asynchronous constructs in the Questa and GHDL simulators.

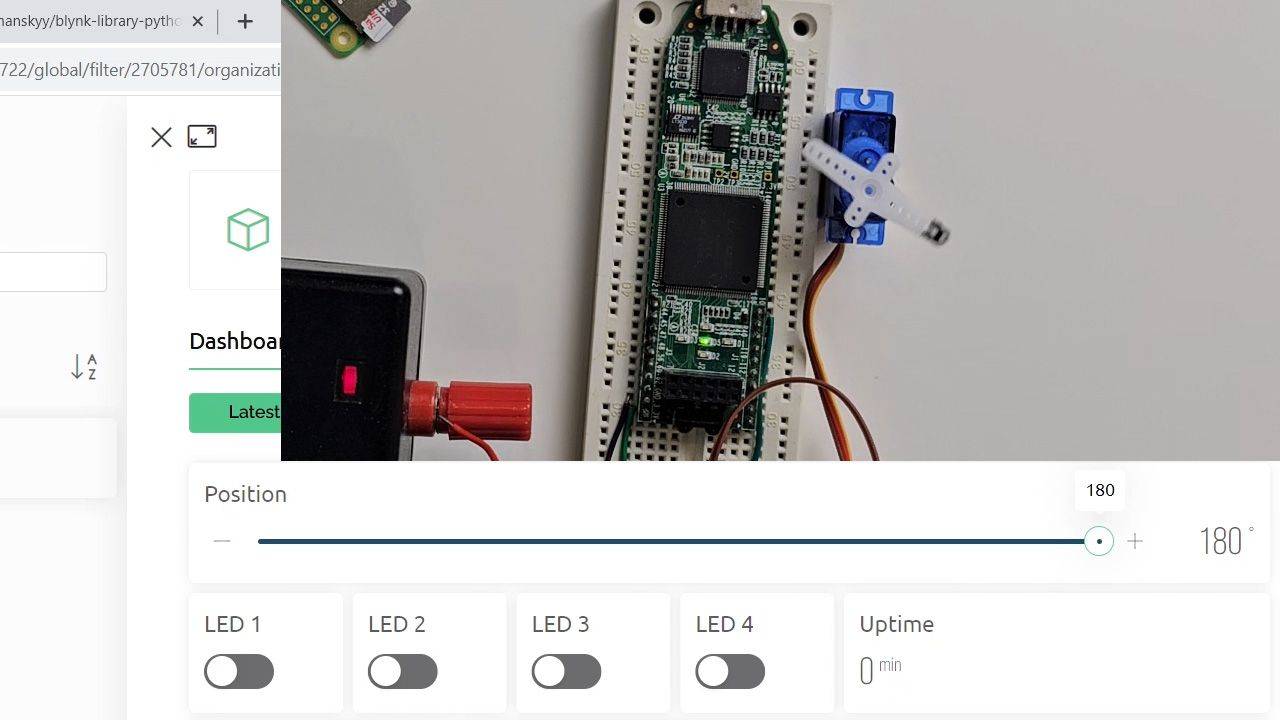

IoT and FPGAs: Building a cloud-connected VHDL design

Bring your VHDL project online. Set up a neat GUI dashboard using the Blynk IoT platform and a Raspberry Pi and send over-the-air (OTA) updates to your FPGA.

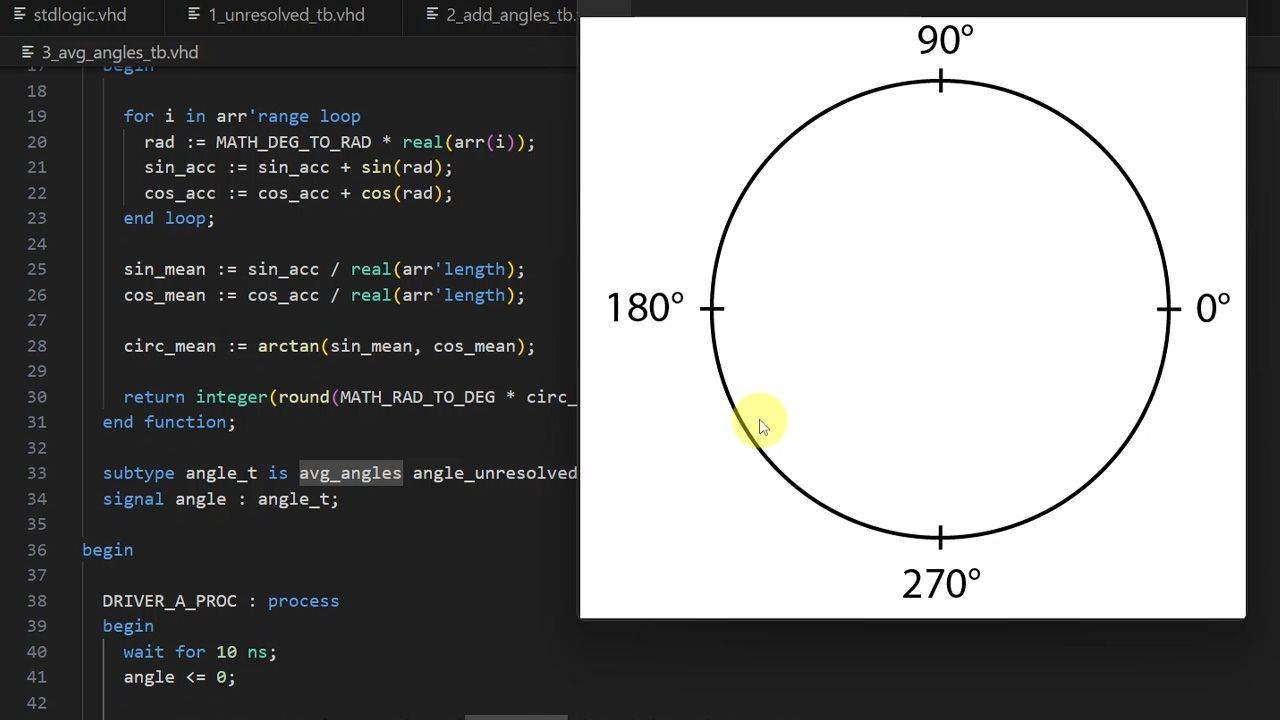

Resolved signals and types with resolution functions in VHDL

Learn how the std_logic type handles driver conflicts internally. See how to implement custom data types with resolution functions for multiple drivers.

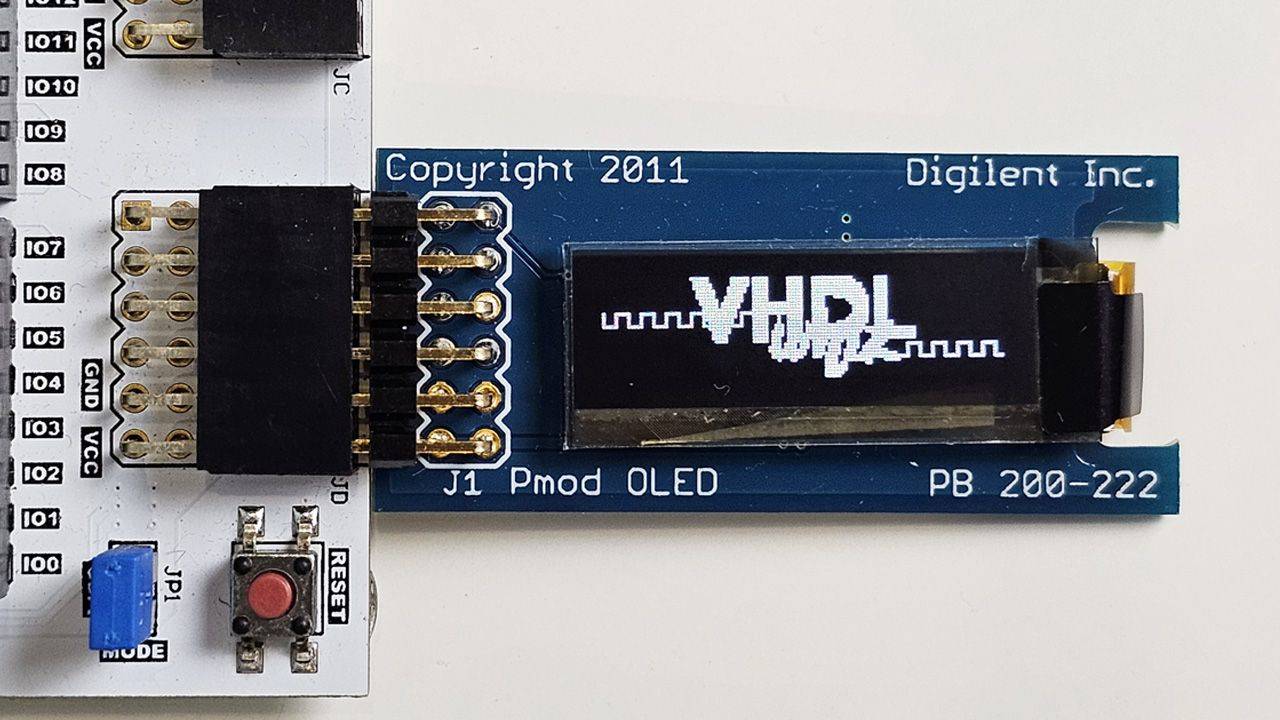

Pmod OLED controller: Display text and graphics with an FPGA

Connect an LED panel to your FPGA design to show messages or images. Create an SPI master and controller module in VHDL. See how to read pixel data from a file into block RAM to update the display.

Signal guards and delays in VHDL

Learn to use guarded blocks to disconnect signal drivers conditionally, and VHDL features like postponed processes and delay modeling mechanisms.

VHDL synthesis: From code to hardware

Learn to recognize which logic elements common VHDL design patterns describe. Think like an FPGA engineer by focusing on the underlying hardware rather than code

VHDL audio mixer using FPGA DSP blocks

Learn to create a 4-input stereo sound mixer using VHDL and multiplier (DSP) primitives in an FPGA. We'll make a neat GUI in Python to control the gain factors in our hardware mixer.

Functional coverage-driven VHDL testbench using UVVM

Learn to implement constrained random testing methods with the UVVM VHDL verification framework. Create self-checking testbenches that discover more corner case bugs.

Snake game on FPGA: Real-time VHDL simulation with GUI

Implement the classic Snake game on an FPGA with a 128×32 OLED display. Create a custom GUI to play the game in real-time using the Questa VHDL simulator.

Transaction-level BFM design in VHDL using Python and AI

Create a bus functional model (BFM) for a VHDL module with multiple configuration options. Learn to make a system that generates custom BFMs for any interface variant the DUT can have.

Source-synchronous data bus: VHDL design and timing constraints for high-speed FPGA interfaces

Design and implement high-speed parallel data buses in FPGAs using VHDL. Gain hands-on experience with timing constraints and experiment with data sampling techniques.

Getting started with PetaLinux

Learn to implement system-on-chip (SoC) designs using embedded Linux for AMD Xilinx FPGAs. This course gives you the skills to succeed with PetaLinux on Zynq-7000 (ARM) devices.

Testbench reuse using VUnit and VHDL configurations for Wishbone bus verification

Learn to combine VHDL configuration statements with VUnit to maximize testbench utilization and automate test case generation, demonstrated through Wishbone master and slave BFM and RTL module DUTs.

QSPI NOR Flash memory VHDL interface

Learn to create a Flash memory controller in VHDL for storing non-volatile data in FPGA projects. This course covers page program (write), read, and erase operations using the quad SPI bus.

Interested in corporate pricing?

Email [email protected] with the number of seats to get an offer.

Alternative payment option

Prepay for access using Bitcoin. Click the button below to learn more.

👇